Reconfigurable Computing

Reconfigurable Computing

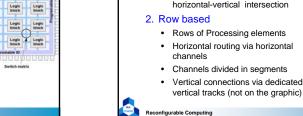

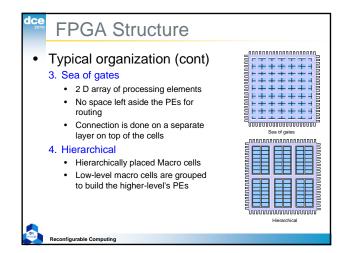

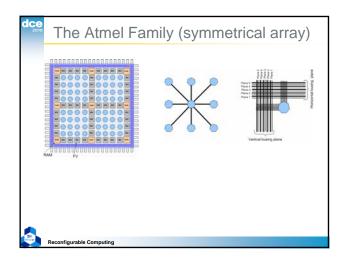

2 D array of processing elements

Interconnection points at the

network

(PE) embedded in an interconnection

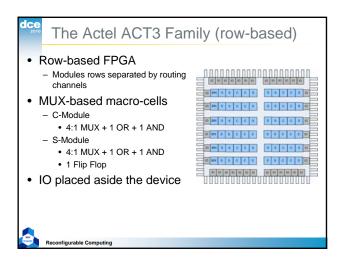

Prov-based

## reconfigurable computing

## reconfigurable computing

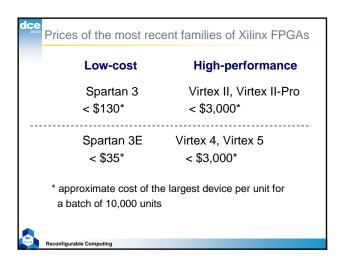

|        | Low-cost                                                                            | High-performance<br>Virtex 4 LX / SX / FX<br>Virtex 5 LX/LXT/SXT/FXT<br>Virtex 6 |  |  |

|--------|-------------------------------------------------------------------------------------|----------------------------------------------------------------------------------|--|--|

| Xilinx | Spartan 3<br>Spartan 3E<br>Spartan 3A<br>Spartan 3AN<br>Spartan 3A DSP<br>Spartan 6 |                                                                                  |  |  |

| Altera | Cyclone II<br>Cyclone III                                                           | Aria II                                                                          |  |  |

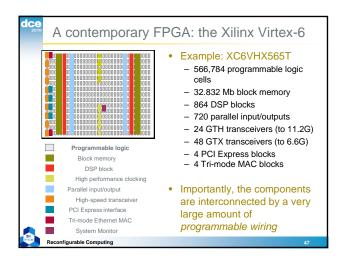

| Criteria            | Stratix<br>IV | Virtex 6        | Virtex 5        | Virtex 5        | Comment                                         |

|---------------------|---------------|-----------------|-----------------|-----------------|-------------------------------------------------|

| Device              | SGX230        | SX315T          | SX240T          | SX95T           |                                                 |

| Price               | 1000 \$       | ?               | 9000 \$         | 1700 \$         |                                                 |

| Process             | 40 nm         | 40 nm           | 65 nm           | 65 nm           |                                                 |

| Clock MHz           | 540           | 600             | 550             | 550             | Multiplier speed                                |

| Nof<br>transceivers | 16 (or<br>24) | 24              | 24              | 16              | Virtex: all on one sid<br>Stratix: on two sides |

| Nof logic           | 91200<br>ALM  | 49500<br>slices | 37440<br>slices | 14720<br>slices | 1 ALM ≈ 0.6 – 0.9 slices                        |

| Nof multipliers     | 1288          | 1344            | 1056            | 640             | Virtex: 25x18<br>Stratix: 18x18 (= 9x           |

| Block RAM           | 14.3 Mb       | 25.3 Mb         | 18.5 Mb         | 8.8 Mb          |                                                 |

| Nof IO              | 560           | 720             | 960             | 640             |                                                 |

| Package pins        | 1152          | 1759            | 1738            | 1136            |                                                 |

| ETH MAC             | Soft core     | 4               | 4               | 4               |                                                 |

## reconfigurable computing