|    | Three categories of limitations have to be considered:                                                                                                                                                                                                                                                                                               |

|----|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

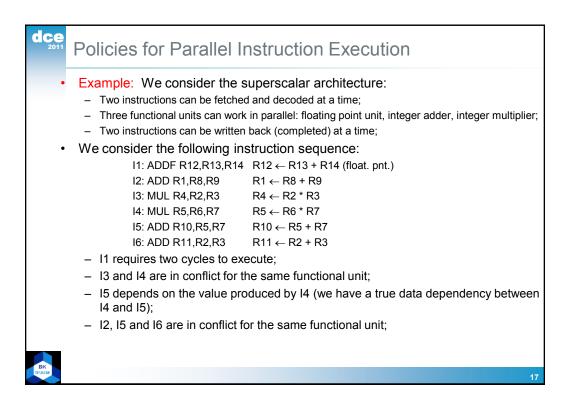

| 1  | Resource conflicts:                                                                                                                                                                                                                                                                                                                                  |

| ١. |                                                                                                                                                                                                                                                                                                                                                      |

|    | <ul> <li>They occur if two or more instructions compete for the same resource (register, men<br/>functional unit) at the same time; they are similar to structural hazards discussed with<br/>pipelines. Introducing several parallel pipelined units, superscalar architectures try to<br/>reduce a part of possible resource conflicts.</li> </ul> |

| 2. | Control (procedural) dependency:                                                                                                                                                                                                                                                                                                                     |

|    | <ul> <li>The presence of branches creates major problems in assuring an optimal parallelism<br/>How to reduce branch penalties has been discussed.</li> </ul>                                                                                                                                                                                        |

|    | <ul> <li>If instructions are of variable length, they cannot be fetched and issued in parallel; ar<br/>instruction has to be decoded in order to identify the following one and to fetch it<br/>bsuperscalar techniques are efficiently applicable to RISCs, with fixed instruction len<br/>and format.</li> </ul>                                   |

| 3. | Data conflicts:                                                                                                                                                                                                                                                                                                                                      |

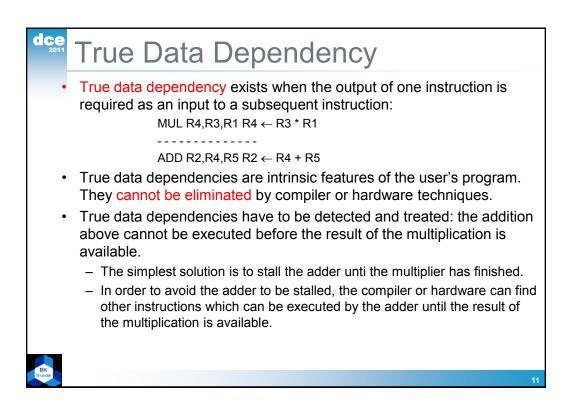

|    | <ul> <li>Data conflicts are produced by data dependencies between instructions in the progra<br/>Because superscalar architectures provide a great liberty in the order in which<br/>instructions can be issued and completed, data dependencies have to be considered<br/>with much attention.</li> </ul>                                           |

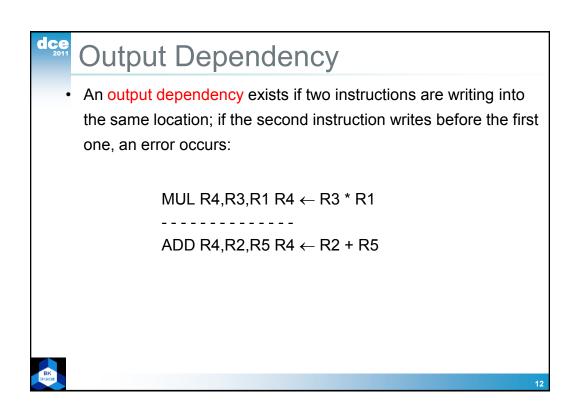

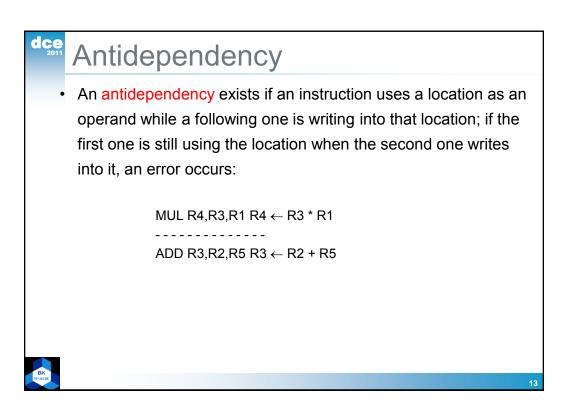

| <b>dce</b><br>2011 | The Nature of Output Dependency and Antidependency                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |  |  |

|--------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

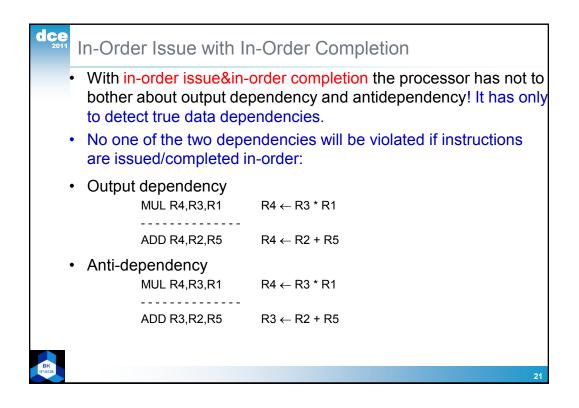

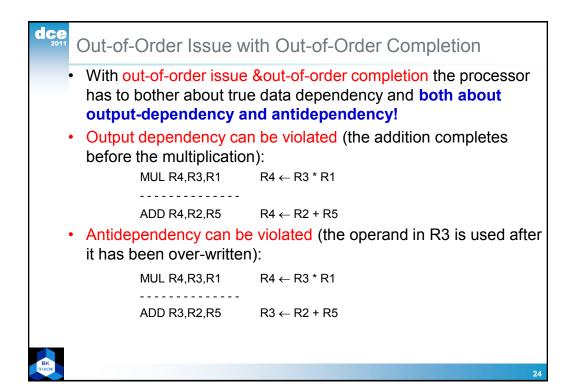

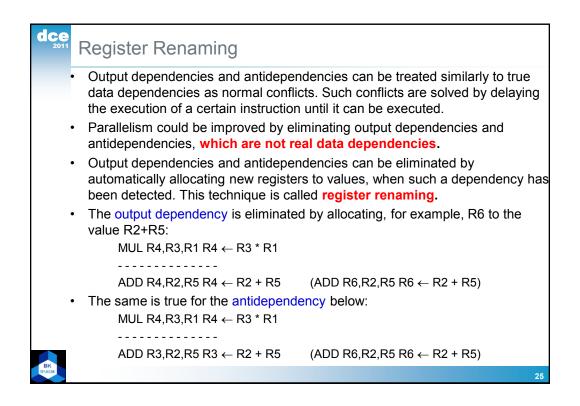

| •                  | Output dependencies and antidependencies are not intrinsic features of the executed program; they are not real data dependencies but storage conflicts. Output dependencies and antidependencies are only the consequence of the manner in which the programmer or the compiler are using registers (or memory locations). They are produced by the competition of several instructions for the same register. In the previous examples the conflicts are produced only because: <ul> <li>the output dependency: R4 is used by both instructions to store the result;</li> </ul> |  |  |

|                    | <ul> <li>the antidependency: R3 is used by the second instruction to store the result;</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |  |  |

| •                  | The examples could be written without dependencies by using additional registers:                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |  |  |

|                    | MUL R4,R3,R1 R4 ← R3 * R1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |  |  |

|                    |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |  |  |

|                    | ADD R7,R2,R5 R7 $\leftarrow$ R2 + R5<br>and                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |  |  |

|                    | MUL R4,R3,R1 R4 ← R3 * R1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |  |  |

|                    |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |  |  |

| ВК                 | ADD R6,R2,R5 R6 ← R2 + R5                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |  |  |

|                    |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |  |  |